Le principal inconvénient du circuit combinatoire c'est-à-dire qu'il n'utilise aucune mémoire pour enregistrer les états actuel et précédent. Par conséquent, l'état antérieur de l'entrée n'a aucun effet sur l'état actuel du circuit. Alors que le circuit séquentiel a une mémoire, la sortie peut donc varier en fonction de l'entrée. Ce type de circuits utilise une entrée, une sortie, une horloge et un élément de mémoire précédents. Ici, les éléments de mémoire peuvent être verrouillés ou bascules. Les circuits séquentiels sont conçus par diverses méthodes telles que l'utilisation de ROM et de flips, de PLA, CPLD (dispositif logique programmable complexe) , FPGA (Field Programmable Gate Array) . Dans cet article, nous allons discuter uniquement de la façon de concevoir un circuit séquentiel à l'aide de PLA.

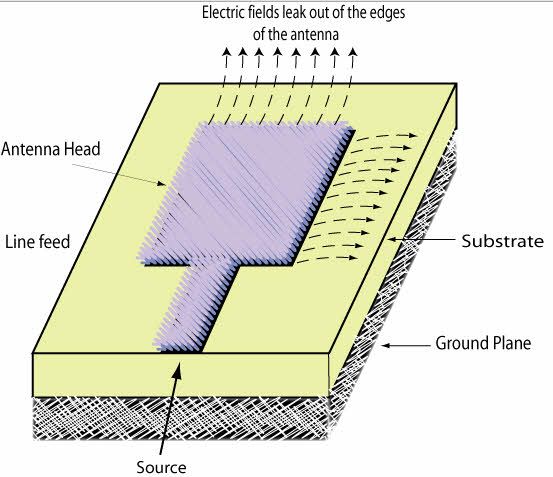

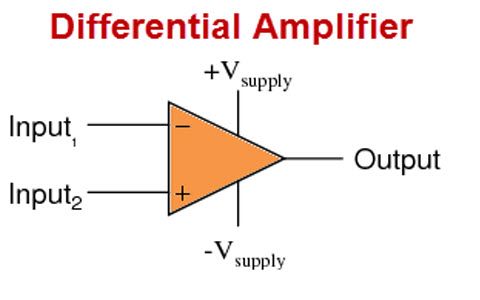

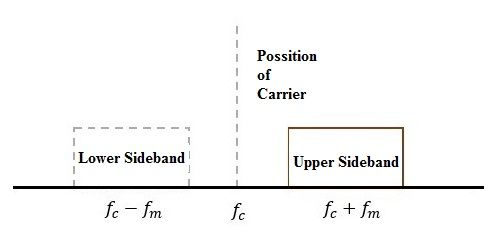

Le schéma de principe du circuit séquentiel comme indiqué ci-dessous:

Schéma fonctionnel du circuit séquentiel

Conception d'un circuit séquentiel à l'aide de PLA

Circuits séquentiels peut être réalisé en utilisant des PLA (Programmable Logic Arrays) et des bascules. Dans cette conception, l'affectation d'état peut être importante car l'utilisation d'une bonne affectation d'état peut réduire le nombre requis de termes de produit et, par conséquent, réduire la taille requise du PLA. Un terme de produit défini comme la conjonction de littéraux, où chaque littéral est soit une variable, soit sa négation.

Car considérons la conception comme un convertisseur de code. Le tableau d'état présenté ci-dessous dans le tableau peut être réalisé en utilisant un PLA et trois tongs comme indiqué ci-dessous. Cette configuration de circuit est très similaire à la conception basée sur une bascule ROM, sauf que la ROM est remplacée par le PLA de taille appropriée. L'affectation de l'état conduit à la table de vérité donnée ci-dessous. Cette table pourrait être stockée dans un PLA avec quatre entrées, 13 termes de produit et quatre sorties, mais cela offrirait une taille peu réduite par rapport à la ROM de 16 mots.

| X Q1 Q2 Q3 | Avec D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1100 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1100 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tableau: Table de vérité

CADEAU ETAT

| ÉTAT SUIVANT X = 0 1 | CADEAU SORTIE (Z) |

| À | AVANT JC | dix |

B C | D E Et E | dix 0 1 |

ré EST | H H H M | 0 1 dix |

H M | A A À - | 0 1 1 - |

Tableau: Tableau des états

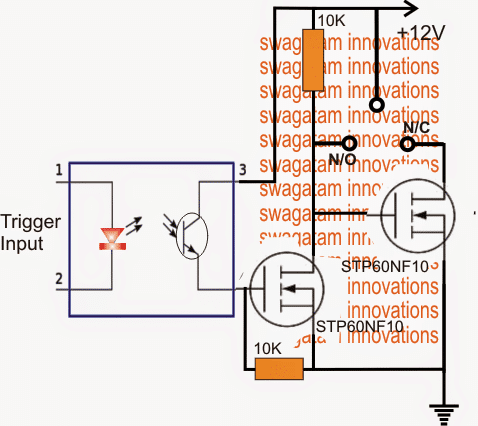

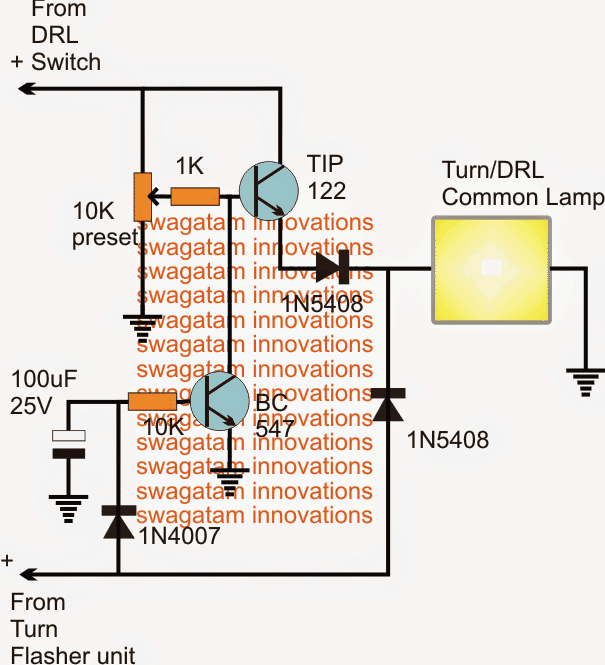

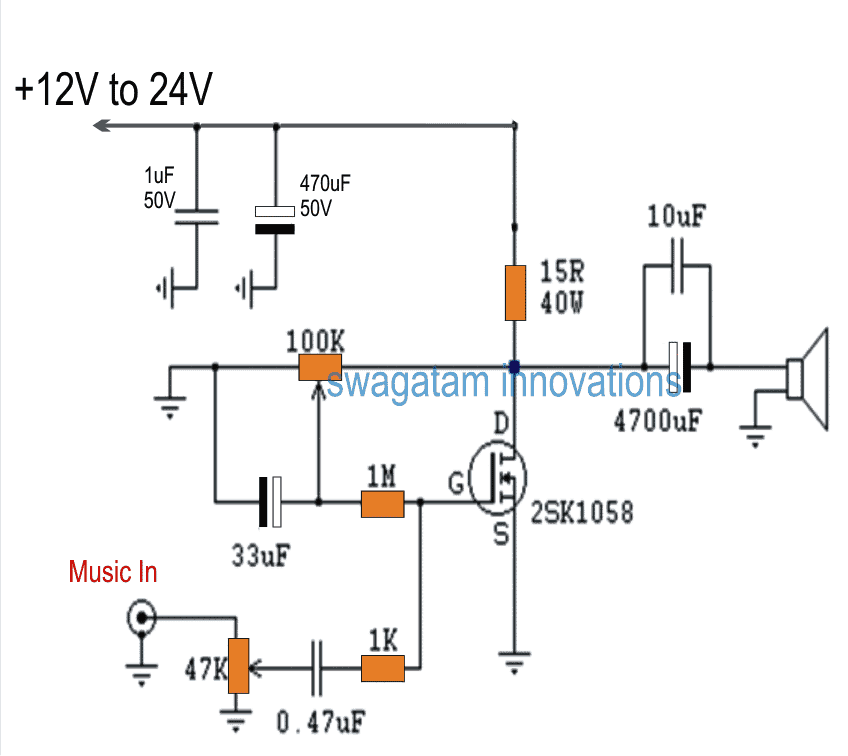

Conception de circuits séquentiels à l'aide de PLA

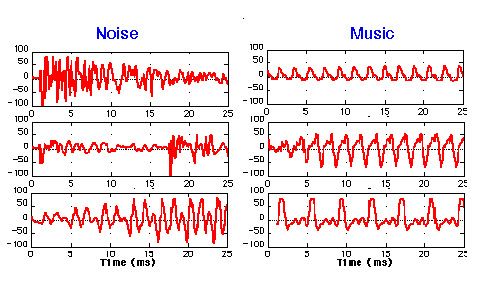

Equations d'entrée-sortie dérivées de la carte de Karnaugh

Ici, comme il y a sept états, trois bascules D sont nécessaires. Ainsi, un circuit PLA avec 4 entrées et 4 sorties est nécessaire. Si l'affectation d'état du convertisseur de code est prise en compte, l'équation de sortie résultante et les équations d'entrée de bascule D dérivées du Karnaugh peuvent être écrites les équations suivantes

D1 = Q1 + = Q2 '

D2 = Q2 + = Q2 '

D3 = Q3 + = Q1 Q2 Q3 = X 'Q1 Q3' = X Q1 'Q2'

Z = X 'Q3' + X Q3

| X Q1 Q2 Q3 | Avec D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 Onze

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Le tableau PLA qui correspond à ces équations est donné dans le tableau ci-dessus. Ce tableau peut être réalisé en utilisant PLA avec quatre entrées, sept termes de produit et quatre sorties. Pour vérifier initialement le fonctionnement de la conception ci-dessus, supposons que X = 0 et Q1Q2Q3 = 000. Ceci sélectionne les lignes - - 0- et 0 - - -0 dans le tableau, donc Z = 0 et D1D2D3 = 100. Après le front d'horloge actif, Q1Q2Q3 = 100. Si l'entrée suivante est X = 1, alors les lignes - - 0 - et - 1- - sont sélectionnées, donc Z = 0 et D1D2D3 = 110. Après le front d'horloge actif, Q1Q2Q3 = 110.

Réseau logique programmable (PLA)

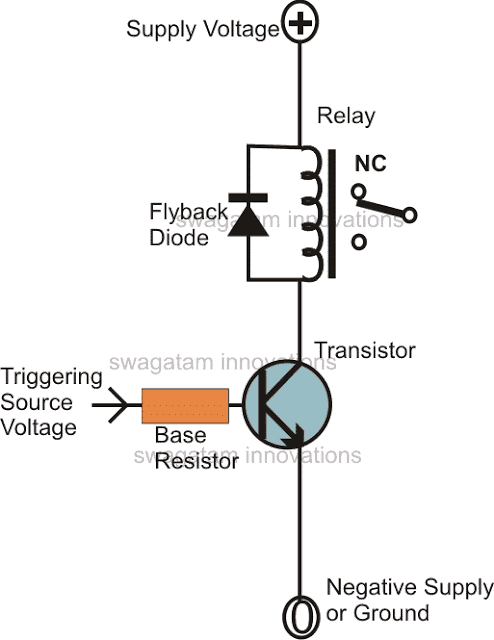

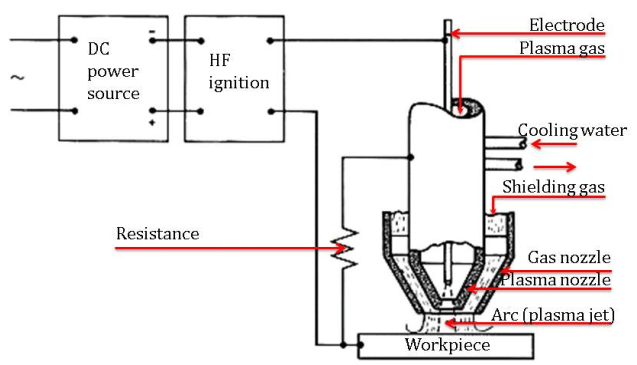

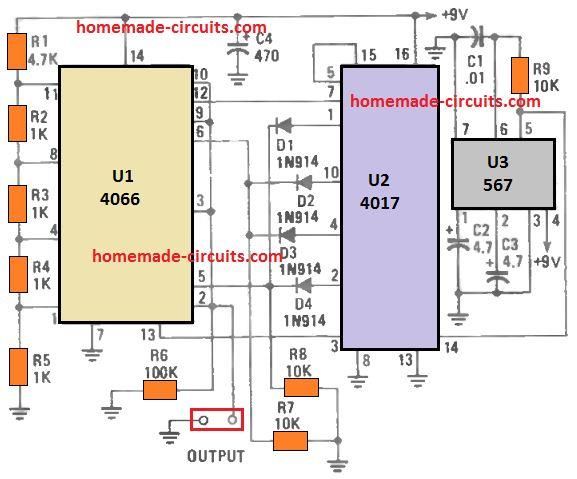

La matrice logique programmable est un périphérique logique programmable. Il est généralement utilisé pour mettre en œuvre des circuits logiques combinatoires. Le PLA a un ensemble de plans ET programmables (matrice ET), qui se lient à un ensemble de plans OU programmables (matrice OU), qui peuvent ensuite être provisoirement complétés pour produire une sortie. Cette disposition permet de synthétiser un grand nombre de fonctions logiques dans le somme des produits (SOP) formes canoniques. Un schéma de principe simple d'un PLA est donné ci-dessous.

Schéma fonctionnel d'un PLA

La principale différence entre PLA et PAL (logique de matrice programmable) est,

PLA: les deux ET avion et OU avion sont programmables.

PAL: Seul le plan AND est programmable, tandis que le plan OR est fixe.

Pour une meilleure compréhension du PLA, nous considérons ici l'exemple ci-dessous.

Essayons d'implémenter ces fonctions f1 et f2 sont données comme

Les entrées x1, x2, x3 et leurs signaux complémentaires respectifs sont donnés au plan ET programmable, là nous obtiendrons des sorties de plan ET comme P1, P2, P3 appelés minterms. Ensuite, ces signaux sont donnés au plan OU programmable pour produire la fonction de sortie requise f1 et f2 (somme des produits). La figure ci-dessous décrit l'implémentation au niveau de la porte du PLA pour une fonctionnalité donnée.

Mise en œuvre du PLA

Il s'agit de la conception de circuits séquentiels à l'aide de PLA. Nous considérons que les informations fournies dans cet article vous sont utiles pour une meilleure compréhension de ce concept. En outre, toute question concernant cet article ou toute aide dans réalisation de projets électriques et électroniques , vous pouvez nous approcher en commentant dans la section commentaires ci-dessous. Voici une question pour vous, Que signifie un circuit séquentiel?