La communication joue un rôle essentiel dans la conception du système embarqué. Sans passer par les protocoles, l'extension périphérique est très complexe et consommatrice d'énergie. Le système embarqué utilise essentiellement la communication série pour communiquer avec les périphériques.

Il existe de nombreux protocoles de communication série, tels que la communication UART, CAN, USB, I2C et SPI. La série protocole de communication les caractéristiques comprennent une vitesse élevée et une faible perte de données. Il facilite la conception au niveau du système et garantit un transfert de données fiable.

Communication de données série

Les informations codées électriquement sont appelées données série, qui sont transmises bit par bit d'un appareil à un autre via un ensemble de protocoles. Dans le système embarqué, des données de capteurs et d'actionneurs de commande sont reçues ou transmises aux dispositifs de commande tels que des microcontrôleurs de sorte que les données soient davantage analysées et traitées. Lorsque les microcontrôleurs travaillent avec les données numériques, les informations du capteurs analogiques , les actionneurs et autres périphériques sont convertis en un mot binaire d'un octet (8 bits) avant d'être transmis au microcontrôleur.

Communication de données série

Ces données série sont transmises par rapport à certaines impulsions d'horloge. Le débit de transmission de données est appelé débit en bauds. Le nombre de bits de données pouvant être transmis par seconde est appelé débit en bauds. Supposons que les données soient de 12 octets, puis chaque octet est converti en 8 bits de sorte que la taille totale de la transmission de données est d'environ 96 bits / s des données (12 octets * 8 bits par octet). Si les données peuvent être transmises une fois par seconde, les vitesses de transmission sont d'environ 96 bits / s ou 96 bauds. L'écran d'affichage actualise la valeur des données une fois par seconde.

Principes de base de l'interface de périphérique série

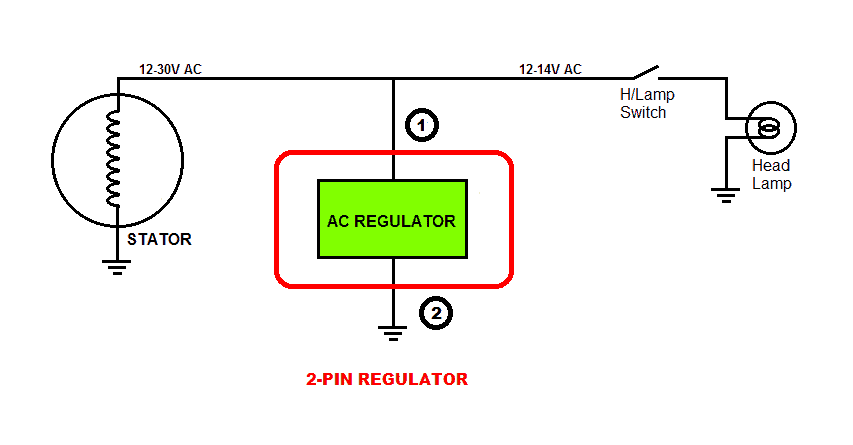

La communication SPI signifie interface périphérique série protocole de communication , qui a été développé par Motorola en 1972. L'interface SPI est disponible sur les contrôleurs de communication courants tels que PIC, AVR et Contrôleur ARM , etc. Il dispose d'une liaison de données de communication série synchrone qui fonctionne en duplex intégral, ce qui signifie que les signaux de données transportent simultanément les deux directions.

Le protocole SPI se compose de quatre fils tels que MISO, MOSI, CLK, SS utilisés pour la communication maître / esclave. Le maître est un microcontrôleur, et les esclaves sont d'autres périphériques comme des capteurs, Modem GSM et modem GPS, etc. Les multiples esclaves sont interfacés avec le maître via un bus série SPI. Le protocole SPI ne prend pas en charge la communication multi-maître et il est utilisé sur une courte distance dans une carte de circuit imprimé.

Principes de base de l'interface de périphérique série

Lignes SPI

MISO (Master en sortie esclave) : La ligne MISO est configurée comme entrée dans un appareil maître et comme sortie dans un appareil esclave.

MOSI (entrée maître sortie esclave) : Le MOSI est une ligne configurée comme une sortie dans un appareil maître et comme une entrée dans un appareil esclave dans laquelle il est utilisé pour synchroniser le mouvement des données.

SCK (horloge série) : Ce signal est toujours piloté par le maître pour un transfert de données synchrone entre le maître et l'esclave. Il est utilisé pour synchroniser le mouvement des données entrant et sortant via les lignes MOSI et MISO.

SS (Slave Select) et CS (Chip Select) : Ce signal est piloté par le maître pour sélectionner des esclaves / périphériques individuels. C'est une ligne d'entrée utilisée pour sélectionner les appareils esclaves.

Communication maître-esclave avec bus série SPI

Implémentation SPI mono-maître et mono-esclave

Ici, la communication est toujours initiée par le maître. Le dispositif maître configure d'abord la fréquence d'horloge qui est inférieure ou égale à la fréquence maximale prise en charge par le dispositif esclave. Le maître sélectionne ensuite l'esclave souhaité pour la communication en faisant glisser la ligne de sélection de puce (SS) de ce dispositif esclave particulier pour passer à l'état bas et actif. Le maître génère les informations sur la ligne MOSI qui transporte les données du maître à l'esclave.

Communication maître-esclave

Implémentations à un seul maître et à plusieurs esclaves

Il s'agit d'une configuration à plusieurs esclaves avec un maître et plusieurs esclaves via le bus série SPI. Les multiples esclaves sont connectés en parallèle à l'appareil maître avec le bus série SPI. Ici, toutes les lignes d'horloge et les lignes de données sont connectées ensemble, mais la broche de sélection de puce de chaque périphérique esclave doit être connectée à une broche de sélection esclave distincte sur le périphérique maser.

Un seul maître et plusieurs esclaves

Dans ce processus, la commande de chaque dispositif esclave est effectuée par une ligne de sélection de puce (SS). La broche de sélection de puce passe au niveau bas pour activer le périphérique esclave et au niveau haut pour désactiver le périphérique esclave.

Le transfert de données est organisé en utilisant les registres à décalage des dispositifs maître et esclave avec une taille de mot donnée d'environ 8 bits et 16 bits, respectivement. Les deux dispositifs sont connectés en anneau de sorte que la valeur du registre à décalage maser soit transmise via la ligne MOSI, puis l'esclave décale les données dans son registre à décalage. Les données sont généralement décalées avec le MSB en premier et le nouveau LSB est décalé dans le même registre.

Transfert de données entre maître et esclave

Importance de la polarité et de la phase de l'horloge

Généralement, la transmission et la réception des données sont effectuées par rapport aux impulsions d'horloge aux fronts montants et descendants. Les microcontrôleurs avancés ont deux fréquences: la fréquence interne et la fréquence externe. Des périphériques SPI pourraient être ajoutés en partageant les lignes MISO, MOSI et SCLK. Les périphériques sont de types ou de vitesses différents comme ADC, DAC, etc. Nous devons donc modifier les paramètres SPCR entre les transferts vers différents périphériques.

Registre SPCR

Le bus SPI fonctionne dans l'un des 4 modes de transfert différents avec une polarité d'horloge (CPOL) et une phase d'horloge (CPHA) qui définit un format d'horloge à utiliser. La polarité d'horloge et les fréquences d'horloge de phase dépendent du périphérique que vous essayez de communiquer avec le maître.

CPHA = 0, CPOL = 0: Le premier bit démarre comme un signal inférieur - les données sont échantillonnées au front montant et les données changent sur front descendant.

CPHA = 0, CPOL = 1: Le premier bit commence par une horloge inférieure - les données sont échantillonnées au front descendant et les données changent sur front montant.

CPHA = 1, CPOL = 0: le premier bit démarre avec une horloge plus élevée - les données sont échantillonnées au front descendant et les données changent sur front montant.

CPHA = 1, CPOL = 1: Le premier bit démarre avec une horloge plus élevée - les données sont échantillonnées au front montant et les données changent sur front descendant.

Horaires du bus SPI

Protocole de communication SPI

De nombreux microcontrôleurs ont des protocoles SPI intégrés qui gèrent toutes les données d'envoi et de réception. Toutes les opérations en mode données (R / W) sont contrôlées par un contrôle et des registres d'état du protocole SPI. Ici, vous pouvez observer l'interface EEPROM vers le microcontrôleur PIC16f877a via le protocole SPI.

Ici, 25LC104 EEROM est une mémoire de 131072 octets dans laquelle le microcontrôleur transfère deux octets de données au Mémoire EEROM via un bus série SPI. Le programme de cette interface est donné ci-dessous.

Communication maître-esclave via le bus série SPI

#comprendre

Sbit SS = RC ^ 2

Sbit SCK = RC ^ 3

Sbit SDI = RC ^ 4

Sbit SDO = RC ^ 5

Annuler initialiser EEROM ()

Void principal ()

{

SSPSPAT = 0x00

SSPCON = 0x31

SMP = 0

SCK = 0

SDO = 0

SS = 1

EE_adress = 0x00

SPI_write (0x80)

SPI_écriture (1234)

SS = 0

}

Avantages du protocole SPI

- Il s'agit d'une communication en duplex intégral.

- Il s'agit d'un bus de données haute vitesse 10 MHz.

- Il n'est pas limité à 8 bits lors du transfert

- L'interfaçage matériel est simple via SPI.

- L'esclave utilise une horloge maître et n'a pas besoin d'oscillateurs précieux.

Tout cela concerne les communications SPI et ses interface avec un microcontrôleur . Nous apprécions votre vif intérêt et votre attention pour cet article et anticipons donc votre point de vue sur cet article. De plus, pour tout codage d'interfaçage et assistance, vous pouvez nous le demander en commentant ci-dessous.

Crédits photo:

- Communication de données série par Glowscotland

- Principes de base de l'interface de périphérique série par ni

- Un seul maître et plusieurs esclaves par manger

- Transfert de données entre maître et esclave par ingénieur garage

- Horaires du bus SPI par maximintegrated

![Circuit de détecteur de phase CA sans contact [testé]](https://electronics.jf-parede.pt/img/sensors-detectors/38/non-contact-ac-phase-detector-circuit.png)